## Chapter 5

Logic Design with MSI Components and Programmable Logic Devices

## The complexity of a chip

#### Scale of integration:

- SSI 1 10 gates

- MSI 10 100 gates

- LSI 100 1000 gates

- VLSI > 1000 gates

J. C. Huang, 2004 Digital Logic Design

## Specialized MSI components

- · adders

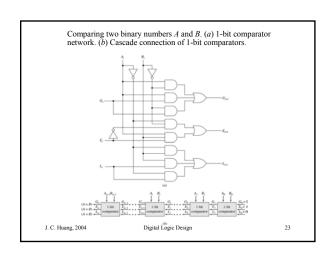

- comparators

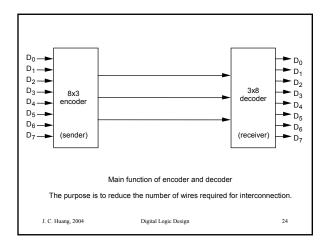

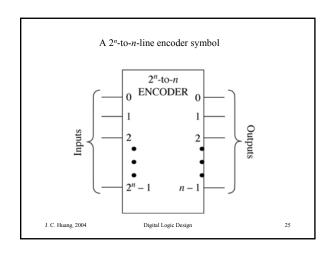

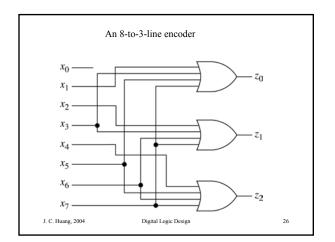

- · encoders/decoders

- multiplexers/demultiplexers

J. C. Huang, 200-

Digital Logic Design

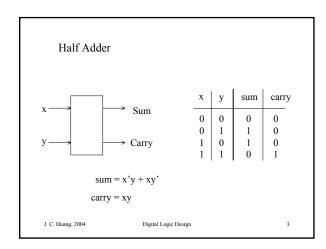

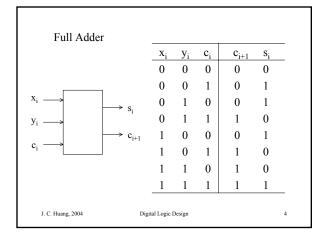

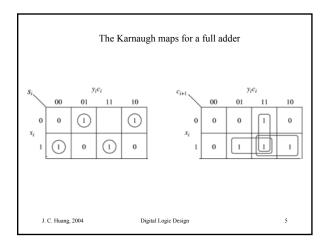

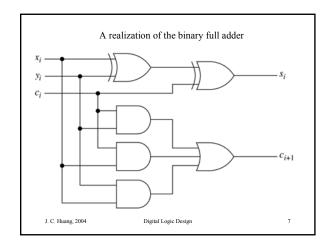

### SUM and CARRY functions

$$SUM = x'y'c + x'yc' + xy'c' + xyc$$

$$CARRY = xy + yc + cx$$

J. C. Huang, 2004

Digital Logic Design 6

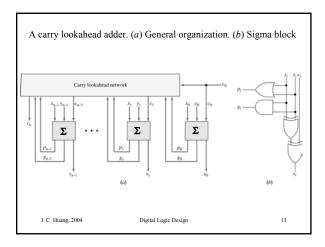

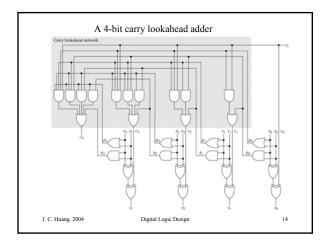

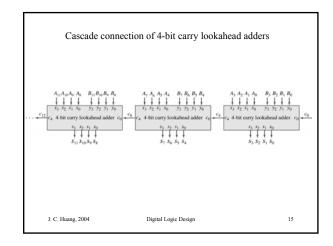

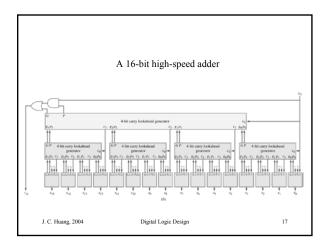

## Carry-look-ahead adder

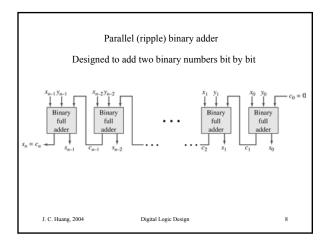

- Problem: the time required to do addition is proportional to the number of bits involved.

- Solution: compute the carry for each stage independently by using a carry-look-ahead network.

J. C. Huang, 2004

Digital Logic Design

11

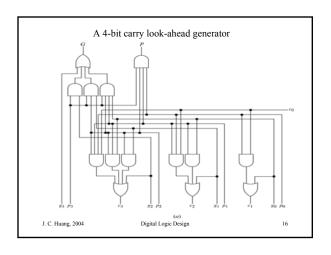

# Carry-Look-ahead Adder

Recall that

$c_{i+1} = x_i y_i + x_i c_i + y_i c_i = x_i y_i + (x_i + y_i) c_i$

Let  $g_i = x_i y_i$  be the *carry-generate* function, and

$p_i = x_i + y_i$  be the *carry-propagate* function.

Then we can write  $c_{i+1} = g_i + p_i c_i$  and

$c_1^{} = g_0^{} + p_0^{} c_0^{}$

$\boldsymbol{c}_2 = \boldsymbol{g}_1 + \boldsymbol{p}_1 \boldsymbol{g}_0 + \boldsymbol{p}_1 \boldsymbol{p}_0 \boldsymbol{c}_0$

$c_3 = g_2 + p_2 g_1 + p_2 p_1 g_0 + p_2 p_1 p_0 c_0$

We see that all carry signal  $c_i$  can be computed by a two level logic circuit.

J. C. Huang, 2004

Digital Logic Design

12

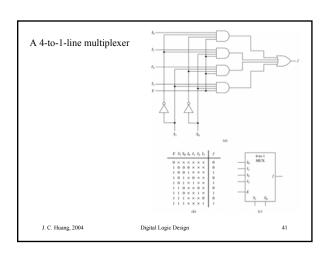

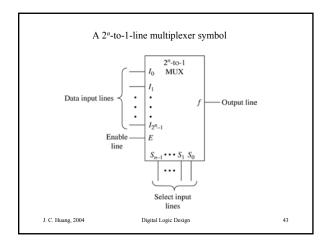

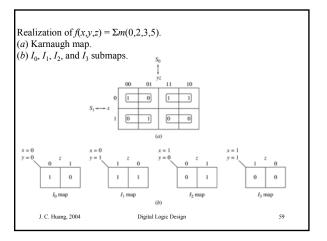

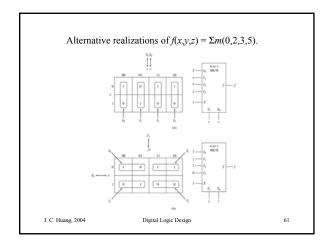

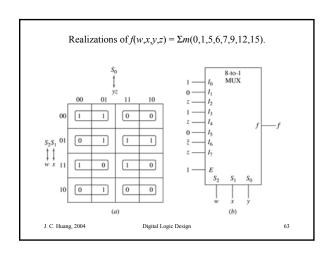

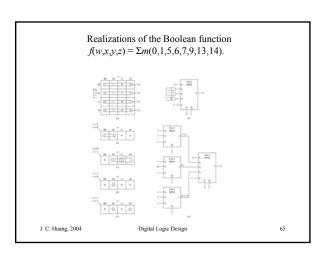

#### MUX implementation of a Boolean function

Any Boolean function of n variables can be implemented by a multiplexer with n control inputs in a straightforward manner.

J. C. Huang, 2004 Digital Logic Design

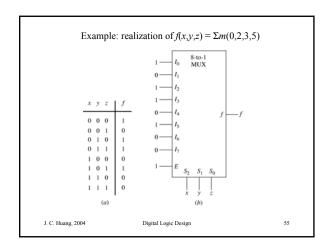

Example:  $f(x, y, z) = \Sigma m(2, 5, 6, 7)$  $y z \mid f(x, y, z)$  $0 \ 0 \ 0 \ | \ f(0,0,0)$ 0 0 1 f(0, 0, 1)1 0 f(0, 1, 0)1 1 1 f(0, 1, 1)0 0 0 f(1, 0, 0)0 1 f(1, 0, 1) $1 \ 1 \ 0 \ | \ f(1, 1, 0)$ 1 1 1 1 | f(1, 1, 1) 45

#### MUX implementation of a Boolean function

44

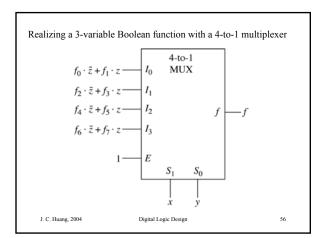

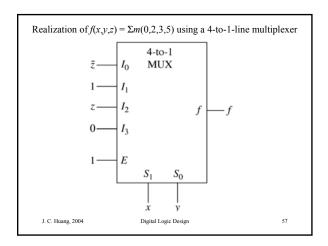

• Even better, any Boolean function of n variables can be implemented by a multiplexer with n-1 control inputs as illustrated in the following.

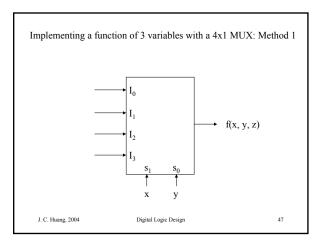

Using a multiplexer to implement a Boolean function: Method 1

Note that the output of a 4x1 multiplexer is

$$F(x, y, z) = x'y'I_0 + x'yI_1 + xy'I_2 + xyI_3$$

Now, given a Boolean function

$$\begin{array}{l} f(x,y,z) = f(0,0,0)x'y'z' + f(0,1,0)x'yz' + f(1,0,0)xy'z' + f(1,1,0)xyz' \\ + f(0,0,1)x'y'z + f(0,1,1)x'yz + f(1,0,1)xyz + f(1,1,1)xyz \end{array}$$

J. C. Huang, 2004

Digital Logic Design

48

52

The value for input I<sub>0</sub> is to be determined as follows.

|                 | * *              |                         |                      |

|-----------------|------------------|-------------------------|----------------------|

| if f(0, 0, 0) = | and f(0, 0, 1) = | then f(0, 0, 0)x'y'z' + | and thus we should   |

|                 |                  | f(0, 0, 1)x'y'z =       | let I <sub>0</sub> = |

| 0               | 0                | 0=x'y'0                 | 0                    |

| 0               | 1                | x'y'z                   | z                    |

| 1               | 0                | x'y'z'                  | z'                   |

| 1               | 1                | x'y'=x'y'1              | 1                    |

The value for I1, I2, and I3 are to be determined in a similar manner.

J. C. Huang, 2004

Digital Logic Design

49

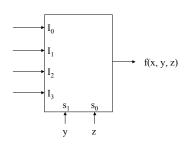

Implementing a function of 3 variables with a 4x1 MUX: Method 2

J. C. Huang, 2004

Digital Logic Design

Using a multiplexer to implement a Boolean function: Method 2

Note that the output of a 4x1 multiplexer is

$$F(x, y, z) = I_0y'z' + I_1y'z + I_2yz' + I_3yz$$

Now, given a Boolean function

$$\begin{array}{l} f(x,y,z) = f(0,0,0)x'y'z' + f(0,0,1)x'y'z + f(0,1,0)x'yz' + f(0,1,1)x'yz \\ + f(1,0,0)xy'z' + f(1,0,1)xy'z + f(1,1,0)xyz' + f(1,1,1)xyz \end{array}$$

J. C. Huang, 2004

Digital Logic Design

The value for input I<sub>0</sub> is to be determined as follows.

| if f(0, 0, 0) = | and f(0, 0, 1) = | then f(0, 0, 0)x'y'z' + | and thus we should   |

|-----------------|------------------|-------------------------|----------------------|

|                 |                  | f(1, 0, 0)xy'z' =       | let I <sub>0</sub> = |

| 0               | 0                | 0=0y'z'                 | 0                    |

| 0               | 1                | xy'z'                   | х                    |

| 1               | 0                | x'y'z'                  | x'                   |

| 1               | 1                | y'z'=1y'z'              | 1                    |

The value for  $I_1$ ,  $I_2$ , and  $I_3$  are to be determined in a similar manner.

J. C. Huang, 2004

Digital Logic Design

A multiplexer tree to form a 16-to-1-line multiplexer

16-to-1-line multiplexer

10-to-1-line multiplexer

10-to-1-line multiplexer

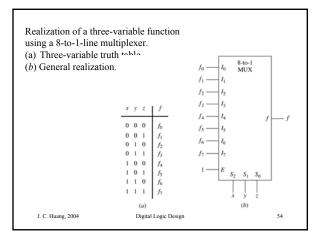

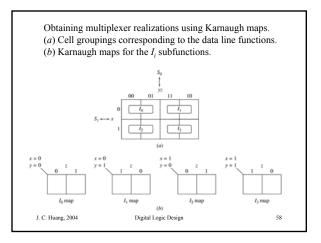

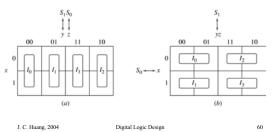

Using Karnaugh maps to obtain multiplexer realizations under various assignments to the select inputs.

(a) Applying input variables y and z to the  $S_1$  and  $S_0$  select lines.

(b) Applying input variables x and y to the  $S_0$  and  $S_1$  select lines.

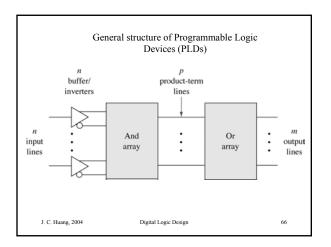

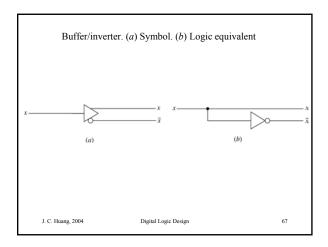

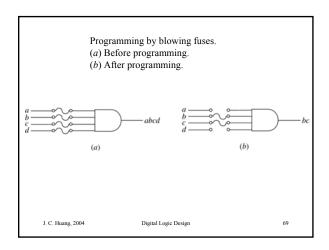

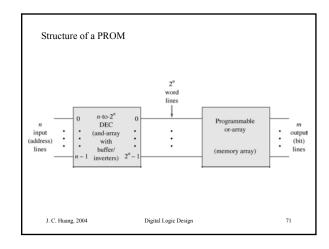

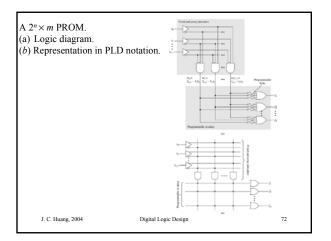

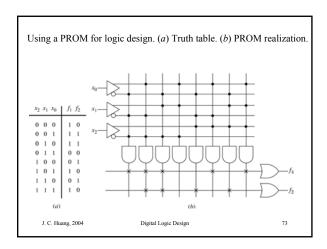

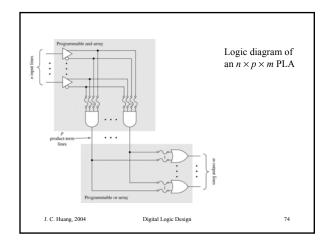

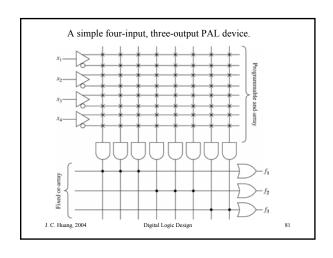

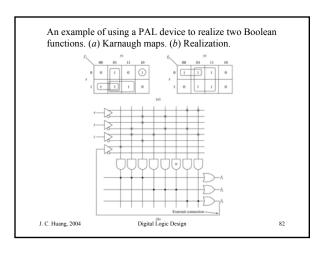

## Types of PLDs

| Device | AND-array    | OR-array     |

|--------|--------------|--------------|

| PROM   | Fixed        | Programmable |

| PLA    | Programmable | Programmable |

| PAL    | Programmable | Fixed        |

## Limitations of PLAs and PALs

These chips are limited to fairly modest size, typically supporting a combined number of inputs plus outputs of not more than 32.

J. C. Huang, 2004 Digitalilogia Design 85

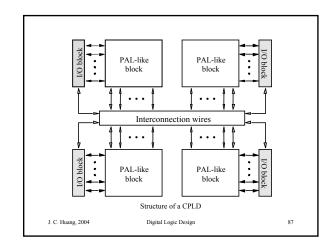

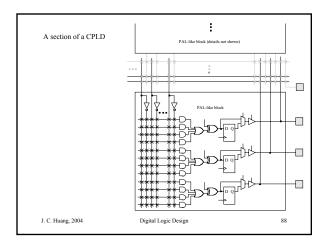

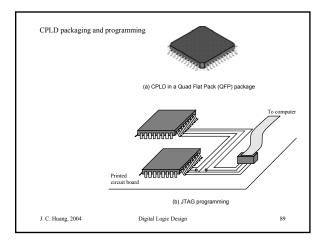

# Complex Programmable Logic Devices (CPLDs)

A CPLD comprises multiple PAL-like blocks on a single chip with internal wiring resources to connect the circuit blocks.

It is made to implement complex circuits that cannot be done on a PAL or PLA.

### A Measure of Circuit Size

A commonly used measure is the total number of two-input NAND gates that would be needed to build the circuit.

It is called the *number of equivalent gates*.

90

J. C. Huang, 2004 Digital Logic Design

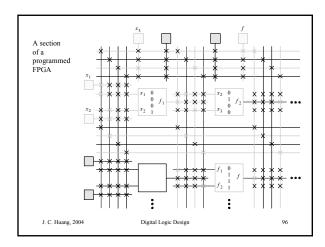

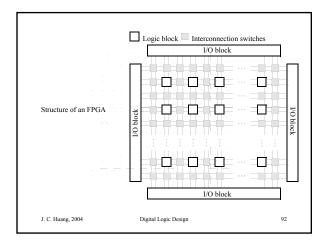

Field-Programmable Gate Arrays (FPGAs)

An FPGA is a PLD that supports implementation of large logic circuits.

It is different from others in that it does not contain AND or OR planes. Instead, it contains logic blocks as depicted in the next slide.

J. C. Huang, 2004 Digital Logic Design 91

## Typical FPGAs

FPGAs can be used to implement logic circuits of more than a few hundred thousand equivalent gates in size.

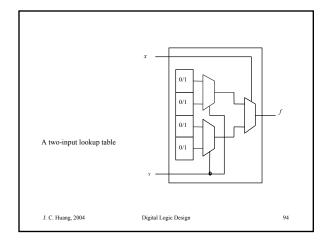

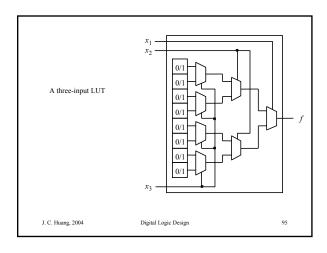

The most commonly used logic block is a *lookup table (LUT)* as depicted in Fig. 3.36.

Slide 3.35.1